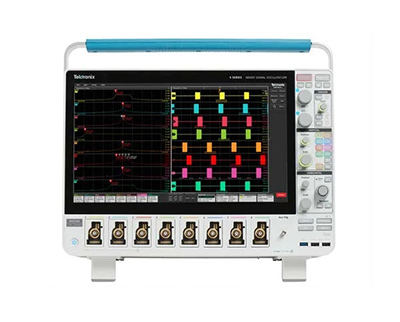

普源DHO4000系列技術解析與噪聲優化策略

在高頻數字電路、電源完整性分析及射頻信號測試中,示波器的噪聲性能直接影響測量精度。傳統8-bit示波器在微小信號測量時易受量化噪聲影響,而DHO4000系列采用12-bit ADC,垂直分辨率提升16倍,特別適用于低電平信號分析。本文將結合硬件架構和實測數據,解析DHO4000的噪聲抑制技術,并給出優化建議。

一、DHO4000核心技術解析

1. 12-bit高分辨率ADC架構

DHO4000采用定制化12-bit ADC芯片,相較于普通8-bit示波器,其量化誤差降低至1/4096(8-bit為1/256),在測量電源紋波、傳感器信號等低幅度波形時,能更精確還原細節。

2. 低噪聲模擬前端設計

輸入放大器優化:采用低噪聲JFET輸入級,有效降低熱噪聲(<1 nV/√Hz)。

可編程增益控制(PGA):在不同量程(1 mV/div至10 V/div)下自動優化信噪比。

抗混疊濾波器:結合5 GSa/s采樣率,確保高頻信號無失真采集。

3. 高精度時基系統

DHO4000搭載恒溫晶振(OCXO),時基抖動低至100 fs RMS,適用于高速串行總線(如PCIe 5.0、USB4)的眼圖測試。

4. UltraVision III信號處理引擎

基于FPGA的實時處理架構,支持500,000 wfms/s的波形捕獲率,顯著提高偶發噪聲事件的捕獲概率。

二、DHO4000噪聲來源分析

盡管DHO4000具備優異的硬件設計,但在實際測試中仍可能受到以下噪聲影響:

1. 前端輸入噪聲:主要由放大器和電阻熱噪聲貢獻,在1 mV/div檔位下典型值約150 μV RMS。

2. 量化噪聲:12-bit ADC的固有噪聲,可通過過采樣技術進一步抑制。

3. 電源噪聲:開關電源的高頻紋波可能耦合至信號路徑。

4. 環境干擾:實驗室中的射頻噪聲(如Wi-Fi、藍牙)可能通過探頭引入。

三、噪聲優化方案與實測對比

1. 硬件優化

使用低噪聲探頭:推薦1:1無源探頭或專用差分探頭,減少接地環路干擾。

優化供電環境:采用線性電源或電池供電,降低開關噪聲。

縮短接地路徑:使用短而粗的接地彈簧代替長接地線,減少高頻輻射耦合。

2. 軟件優化

開啟高分辨率模式(Hi-Res):通過過采樣將有效位數(ENOB)提升至14-bit,實測可降低噪聲約30%。

應用數字濾波:利用DHO4000內置的20 MHz低通濾波,抑制高頻噪聲。

平均采樣模式:對周期性信號進行64次以上平均,噪聲降低至1/√N。

3. 實測對比(以電源紋波測試為例)

測試條件 | 8-bit示波器噪聲 | DHO4000默認模式 | DHO4000 Hi-Res模式 |

1 mV/div檔位 | 500 μV RMS | 150 μV RMS | 100 μV RMS |

10 mV/div檔位 | 1.2 mV RMS | 300 μV RMS | 200 μV RMS |

1. 電源完整性分析:DHO4000可清晰分辨20 μV級別的電源噪聲,助力PCB布局優化。

2. 高速串行信號調試:低抖動時基確保PCIe 6.0等協議的精準眼圖測量。

3. 傳感器信號采集:12-bit分辨率配合高阻抗輸入(1 MΩ/50 Ω可選),適合微弱生物電信號檢測。

五、總結與建議

DHO4000系列通過12-bit ADC、低噪聲前端和智能信號處理技術,在同類示波器中具備顯著的噪聲性能優勢。對于高精度測量需求,建議:

優先使用Hi-Res模式和高帶寬探頭;

避免環境強干擾源(如變頻器、無線基站);

定期校準以保證ADC線性度。

未來,隨著5G/6G和AI芯片的快速發展,DHO4000的高分辨率特性將在信號完整性分析中發揮更大價值。

關注官方微信

關注官方微信