羅德施瓦茨ZNA和R&S ZNB網(wǎng)絡(luò)分析儀高頻高速PCB測試

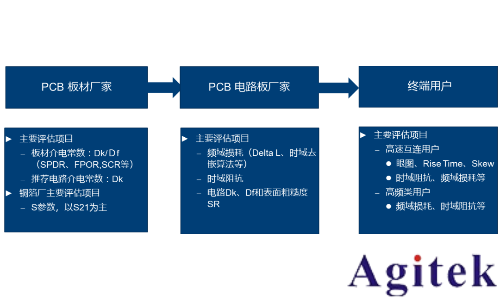

高頻高速PCB廣泛應(yīng)用于AI、高速通信、數(shù)據(jù)中心和消費電子等領(lǐng)域。其性能的穩(wěn)定性和可靠性決定了整個系統(tǒng)的信號完整性和運行效率。高速PCB產(chǎn)業(yè)鏈中的各環(huán)節(jié)緊密相連,共同確保最終產(chǎn)品的質(zhì)量。

高速PCB關(guān)鍵測試指標(biāo)

PCB測試的主要項目包括頻域S參數(shù)、時域阻抗、Rise Time、Skew、眼圖和材料特性等。這些測試項目可以全面評估PCB的傳輸性能、阻抗特性、時序特性以及信號完整性等。

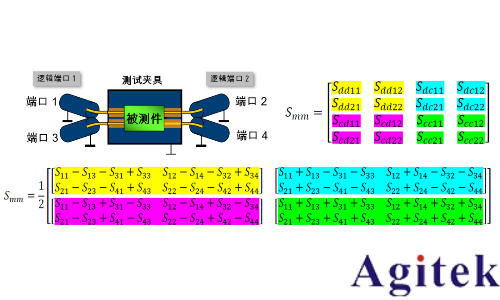

S參數(shù)測試

S參數(shù)測試是高速PCB的常規(guī)測試項目,設(shè)計人員可以通過S參數(shù)來評估PCB線路的傳輸和反射性能。高速PCB特別關(guān)注插入損耗的性能指標(biāo),即Sdd21。Sdd21反映了信號在傳輸過程中的衰減情況,是評估PCB線路性能的關(guān)鍵指標(biāo)。

時域阻抗測試

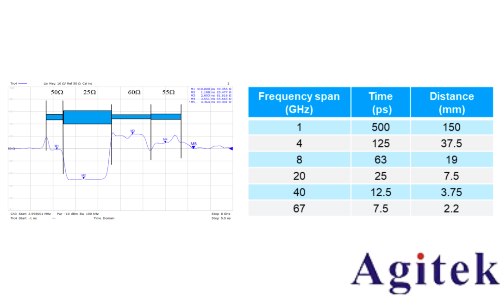

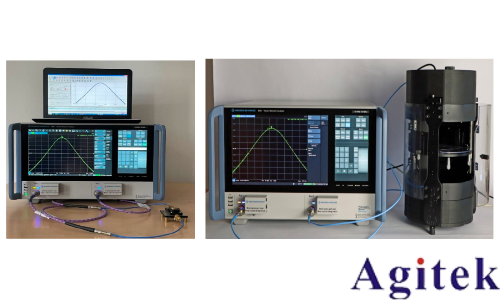

時域阻抗測試是評估高速PCB阻抗特性的重要手段。通過測量PCB的阻抗值,可以了解PCB的傳輸線特性阻抗和阻抗匹配情況等。進行時域阻抗測試時,需要選擇與DUT相匹配的TDR阻抗探頭。探頭型號的選取由測量頻段和PCB走線間距等因素綜合決定。TDR測量的最小時間分辨率近似等于1/(2fmax)。R&S ZNA和R&S ZNB網(wǎng)絡(luò)分析儀都具有時域分析選件(R&S ZNx-K2),用于時域阻抗的測量。

Rise Time測試和Skew測試

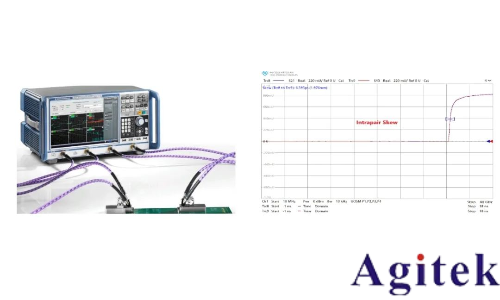

Rise Time測試和Skew測試是評估高速PCB時序特性的重要手段。Rise Time測試可以測量信號的上升時間,從而反映信號的傳輸速度和響應(yīng)時間。Skew測試則可以測量不同信號線之間的時間延遲差異,從而評估信號的同步性和時序準(zhǔn)確性。

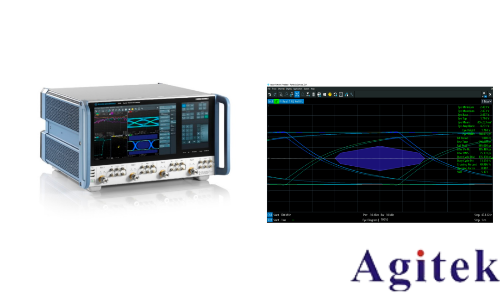

眼圖測試

眼圖測試是評估高速PCB信號完整性的重要手段之一。它可以通過觀察信號的眼圖來評估信號的噪聲、抖動和失真等問題。R&S ZNA和R&S ZNB網(wǎng)絡(luò)分析儀的時域分析擴展選件(R&S ZNx-K20)可以實現(xiàn)PCB的眼圖測量,該選件也具有標(biāo)準(zhǔn)的Rise Time測試和Skew測試功能項。

PCB覆銅板材的Dk/Df測試

PCB覆銅板材的Dk(介電常數(shù))和Df(損耗因子)測試是評估材料介電性能和能量損耗特性的重要手段。測量PCB板材 Dk/Df的常用方法是諧振腔法。根據(jù)測量頻段的不同,諧振腔法又細(xì)分為分離式諧振腔(SPDR)和法布里-珀羅開放式諧振腔 (FPOR)等。SPDR法通常適合于20GHz以下的特性測試,F(xiàn)POR可以實現(xiàn)20-110GHz的特性測試。

介電常數(shù)(Dk):反映PCB基材的介電性能,是影響信號傳輸速度和損耗的重要指標(biāo)。信號的傳輸速率與材料介電常數(shù)的平方根成反比。

損耗因子(Df):用于評估PCB基材的能量損耗,直接影響高頻信號的傳輸性能。介質(zhì)損耗越小,傳輸信號的損耗也越小。

基于PCB傳輸線路的Dk/Df/SR測試

PCB的Dk/Df指標(biāo),除了通過上述所述的諧振腔法之外,還可以通過測量PCB傳輸線段的S參數(shù)特性,再用算法(例如Djordjevic-Sarkar model)反推層壓板材的介電常數(shù)(Dk)和介質(zhì)損耗因子(Df),為覆銅板廠商和PCB制造商提供關(guān)鍵驗收指標(biāo)。

PCB的SR(表面粗糙度)指標(biāo)測試,可以基于Huray表面粗糙度模型對PCB傳輸線段的S參數(shù)進行算法解析得到。Huray粗糙度模型(Huray Surface Roughness Model)是一種用于描述導(dǎo)體表面粗糙度對高頻信號完整性影響的數(shù)學(xué)模型,它主要用于預(yù)測由導(dǎo)體表面粗糙度導(dǎo)致的趨膚效應(yīng)增強和信號損耗增加的問題。

去嵌的應(yīng)用和典型去嵌方法

去嵌的重要性

對于網(wǎng)絡(luò)分析儀測試PCB,夾具去嵌至關(guān)重要。在進行高速PCB測試時,通常需要借助夾具轉(zhuǎn)接或探頭點測才能完成。因此需要通過去嵌技術(shù)來消除夾具對DUT測試結(jié)果的影響。

典型去嵌方法

VNA常見的去嵌方法包括基本去嵌方法、高級時域去嵌方法和專用去嵌方法。基本去嵌方法是網(wǎng)絡(luò)分析儀的基本功能,只適用于較低頻率的應(yīng)用。高級去嵌方法,本質(zhì)上是基于時域的算法軟件。R&S 提供了三種時域去嵌選件:R&S?ZNx-K210 (EZD)、R&S?ZNx-K220 (ISD) 和 R&S?ZNx-K230 (SFD)。通過這些去嵌方法,可對夾具的影響進行精確去除。

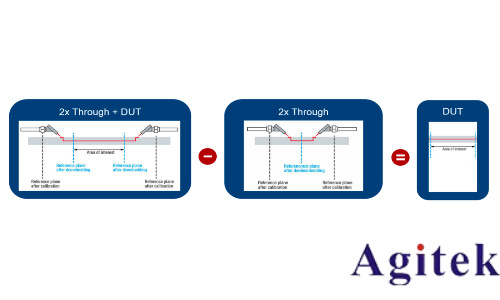

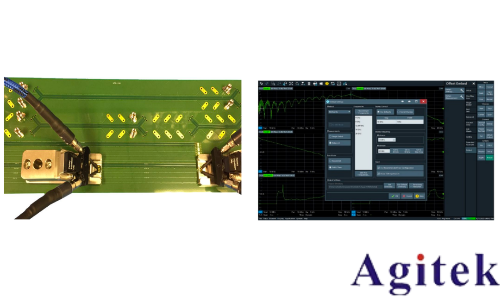

對于PCB產(chǎn)品的測試,還有一些專用的去嵌方法,例如TRL和Delta-L法等。TRL方法相對成熟,在此不再贅述。Delta-L法是由Intel提出的一種基于本征模算法的去嵌方法,當(dāng)前廣泛地用于PCB的插入損耗測試。R&S聯(lián)合Packet micro推出了Delta-L+測量選件R&S ZNx-K231,全面支持Delta-L 4.0測試。該選件支持高達40GHz的測試,滿足Intel的PCB驗證標(biāo)準(zhǔn)。使用Delta-L 4.0測量PCB時,通常需要專用的Delta-L 4.0測量探頭。目前該類探頭的理論上限工作頻率為40GHz。

測試夾具設(shè)計

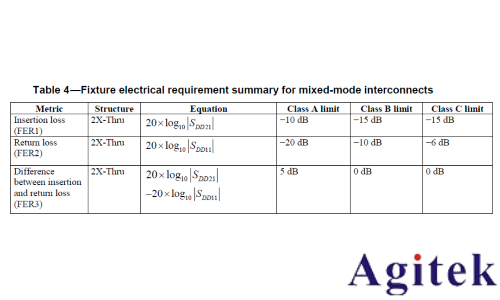

IEEE P370標(biāo)準(zhǔn)規(guī)定了夾具設(shè)計準(zhǔn)則、去嵌驗證步驟與S參數(shù)驗證流程等,以確保去嵌結(jié)果的準(zhǔn)確性和可靠性。測試夾具的設(shè)計對于確保去嵌精度至關(guān)重要。為了保證去嵌精度,夾具的插損和回?fù)p的差值需要滿足一定的條件。下表摘自IEEE Std 370?-2020規(guī)范。

新的挑戰(zhàn)與測試需求

隨著高速技術(shù)的不斷發(fā)展,高頻高速PCB的測試面臨新的挑戰(zhàn)。

挑戰(zhàn)一

PCB的高頻諧振問題

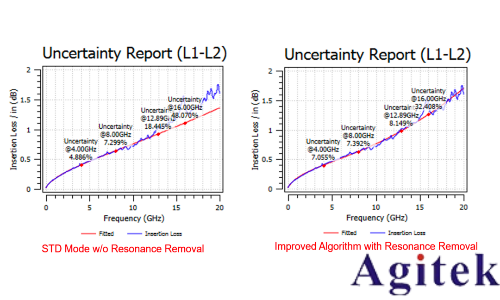

當(dāng)PCB線路在高頻出現(xiàn)諧振時,傳統(tǒng)Delta-L 4.0算法的插損擬合結(jié)果不確定度大幅增加。R&S ZNA-K231 Delta-L+ 選件將在新的固件版本中更新算法,增加PCB抗諧振測試功能,以解決這一問題。當(dāng)DUT在高頻段出現(xiàn)諧振時,新算法將會對諧振頻率以上頻段的測量數(shù)據(jù)重新進行數(shù)學(xué)加權(quán)后再進行擬合,以獲得更更高的擬合精度。下圖為同一DUT(16GHz左右出現(xiàn)諧振)條件下,標(biāo)準(zhǔn)Delta-L 4.0算法和改進算法的擬合結(jié)果對比。

挑戰(zhàn)二

224Gbps 高速PCB的去嵌問題

隨著224Gbps高速互連系統(tǒng)的推出,高速PCB的最高測量頻率將超過67GHz。當(dāng)前Delta-L 4.0標(biāo)準(zhǔn)方法理論上限頻率是40GHz,實際32GHz以上的去嵌精度開始下降。對于40GHz以上的PCB測試,目前較好的去嵌方法還是時域去嵌軟件,例如R&S ISD。但鑒于Delta-L法在PCB行業(yè)的用戶基礎(chǔ)極為廣泛,現(xiàn)在業(yè)界正在致力于67GHz Delta-L測量方案的研究。在更高頻率下,夾具和PCB走線的設(shè)計對測試結(jié)果的影響將更加顯著,67GHz Delta-L測量方案推出前需要解決以下問題。

現(xiàn)有的Delta-L4.0探頭工作頻段不夠,需要67GHz新型號

2*THRU(短線)的長度需要更短以實現(xiàn)損耗更小,從而滿足IEEE P370規(guī)范

2*THRU的EM結(jié)構(gòu)進行仿真優(yōu)化,尤其是跨層過孔的設(shè)計,以獲取更好的匹配

改進當(dāng)前算法,以優(yōu)化高頻抗諧振問題

總 結(jié)

高頻高速PCB測試需綜合考慮材料特性、信號完整性和標(biāo)準(zhǔn)合規(guī)性三大維度。通過依托高精度儀器(如R&S ZNA)和定制化夾具(如Delta-L 4.0專用針座),結(jié)合S參數(shù)、TDR、眼圖等綜合分析方法,以確保PCB的設(shè)計滿足5G、AI及超算等高速應(yīng)用的需求。同時,面對不斷變化的挑戰(zhàn)和趨勢,我們還需要不斷創(chuàng)新和優(yōu)化測試方案,以適應(yīng)未來的技術(shù)發(fā)展和應(yīng)用需求。

關(guān)注官方微信

關(guān)注官方微信